RTLソースコードファイル群を解析してビジュアル化。古いプロジェクトが蘇る。

解析対象の複数の ソースコードファイルまたはフォルダをプロジェクトウィンドウにドロップするだけ。瞬時にブロック図として可視化、解析結果のサマリーを

テキストでレポート出力することができます。

ブロック図は BMP 形式でクリップボードにコピーが可能。あるいは EMF 形式ファイルへエクスポートも可能です。

HDL Auto SpecDraw が持つ機能の概要をここにご紹介します。

複数のソースファイルからなるプロジェクトをブロック図表示

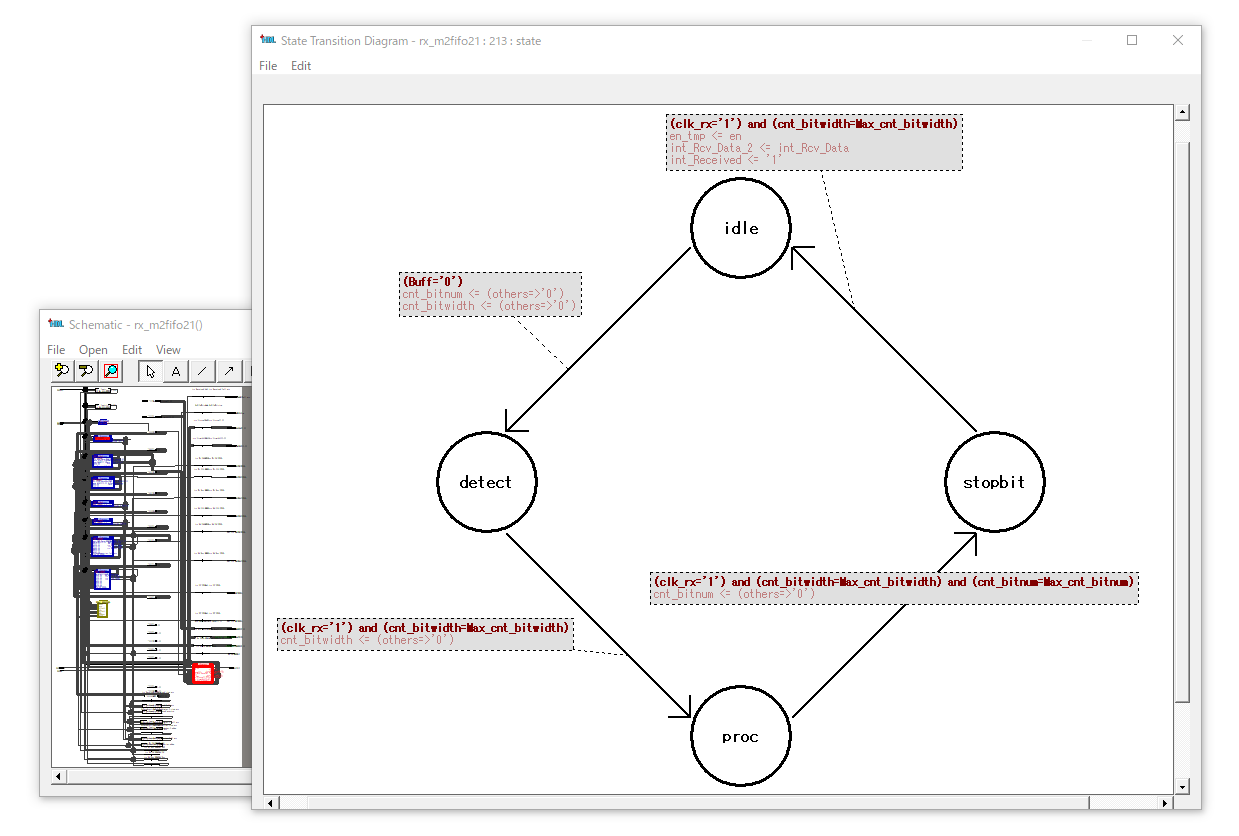

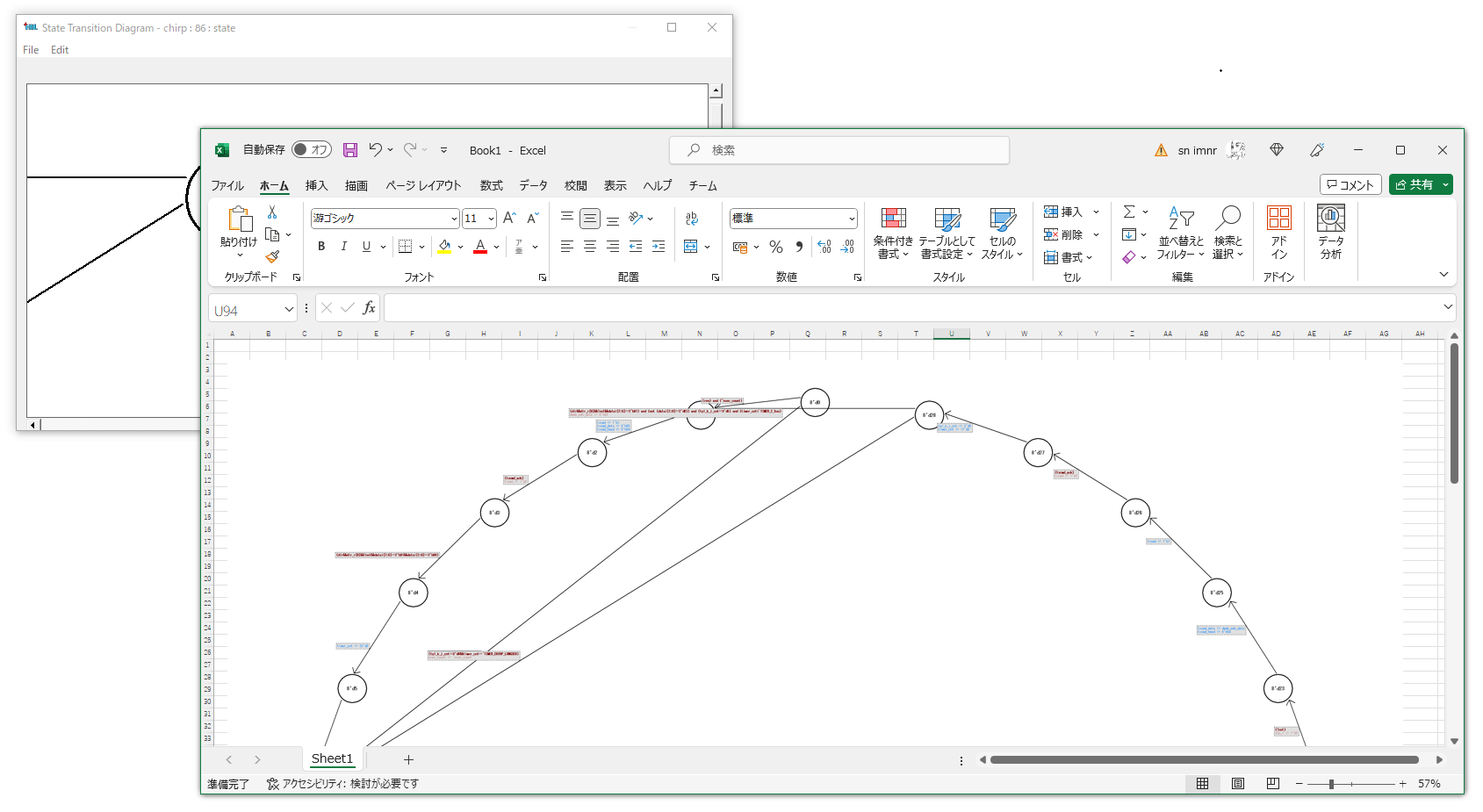

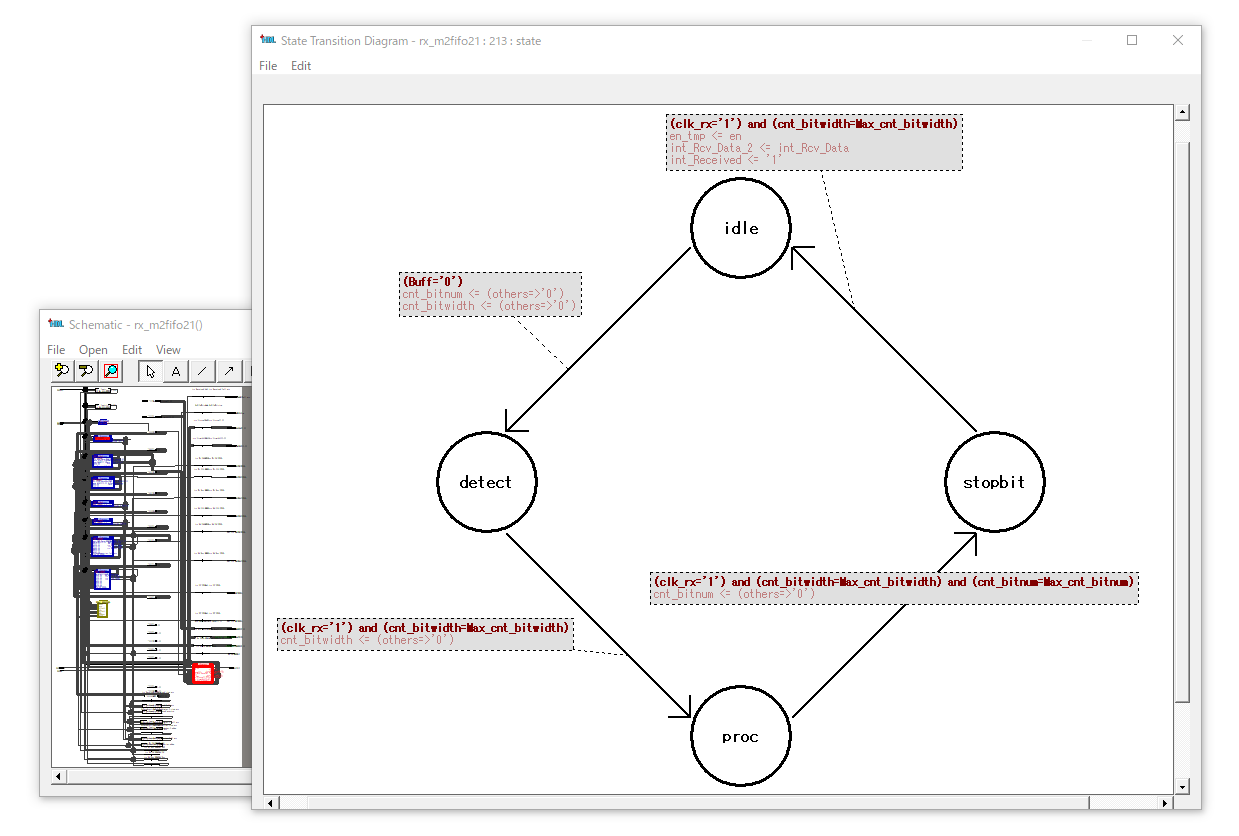

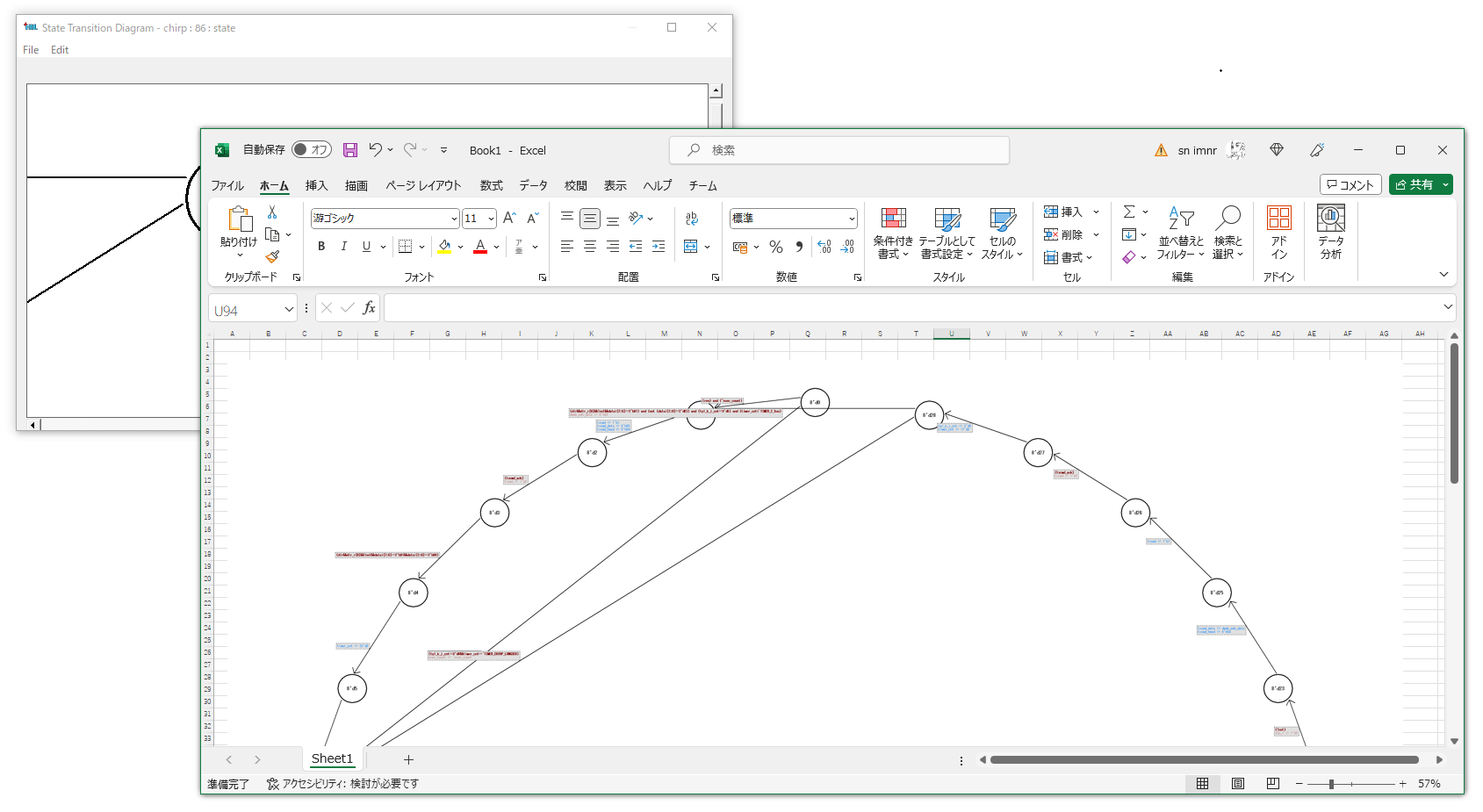

ステートマシンを図でわかりやすく表示

ステートマシンを自動的に検知・解析して表示します

ステートマシンを自動的に検知・解析して表示します

always節(Verilog) / process節(VHDL)では、記述内容をステートマシン図として表示できます。

※case文が解析対象となります。

状態変数、各ステートへの遷移条件、および遷移時に値が変化する信号を、すべて自動的に検出し、図を作成します。

ドキュメントへの貼り付け

BMP 形式でクリップボードへコピーが可能です。

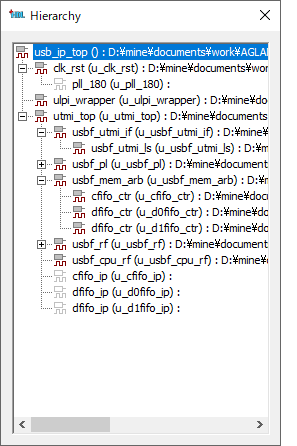

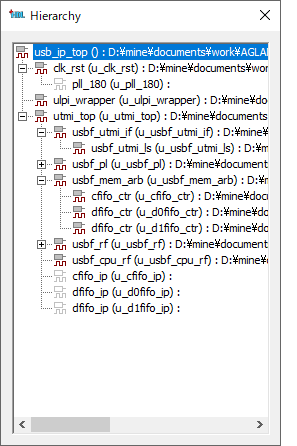

プロジェクトを自動解析、階層構造を表示

ヒエラルキー・ウィンドウには、解析中のプロジェクトのソースコードの階層構造が表示されます。

解析はフルオート。パラメータの類を指定する必要はありません。

不足しているソースコードのファイル名も確認できます。

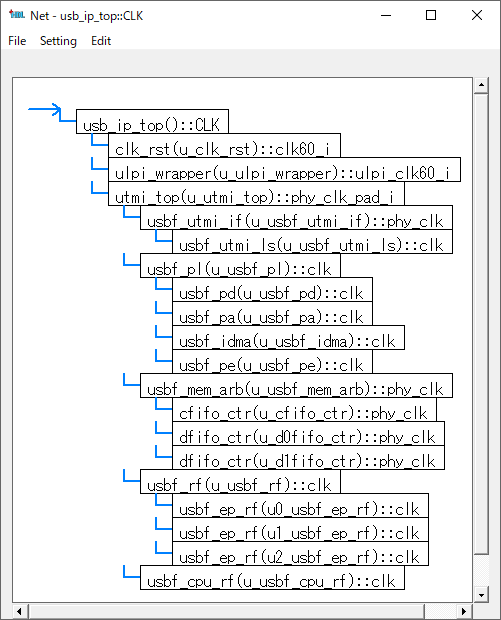

信号の飛び先をまとめて表示するネット機能

指定の信号の飛び先(入力への接続先)をまとめてネット表示。

複雑なブロック図を逐一トレースする必要はありません。

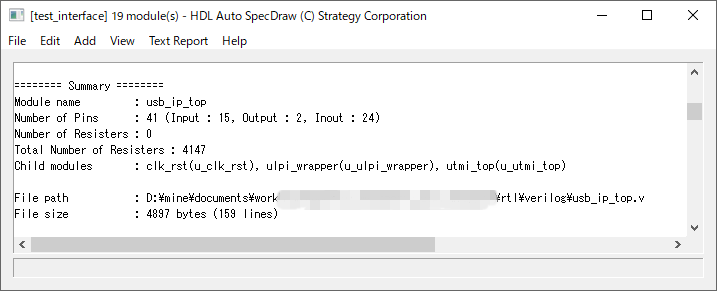

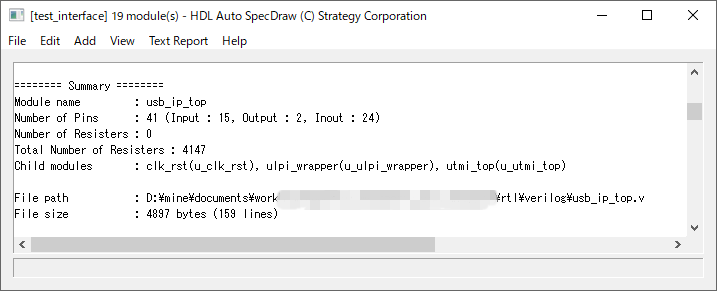

充実のテキスト・レポート

ソースコードで使用しているレジスタ数のレポート機能で、回路規模を簡単に見積もり。下位モジュールのインスタンスの分も合算されますので、見積もりサイズを誤ることもありません。

他にも、特定の信号の接続や、階層構造なども、テキスト形式でレポート可能です。

Verilog HDL / VHDL 混在プロジェクトに対応

Verilog HDL と VHDL が混在したプロジェクトを解析可能。ユーザーは特に意識することなく、すべてツールが自動認識します。

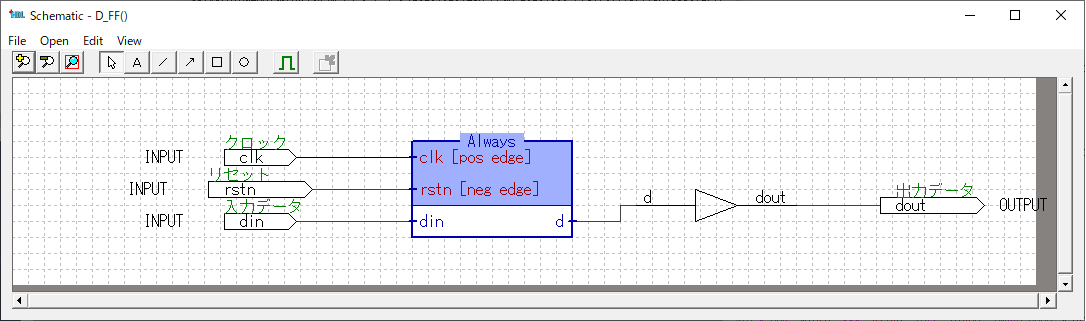

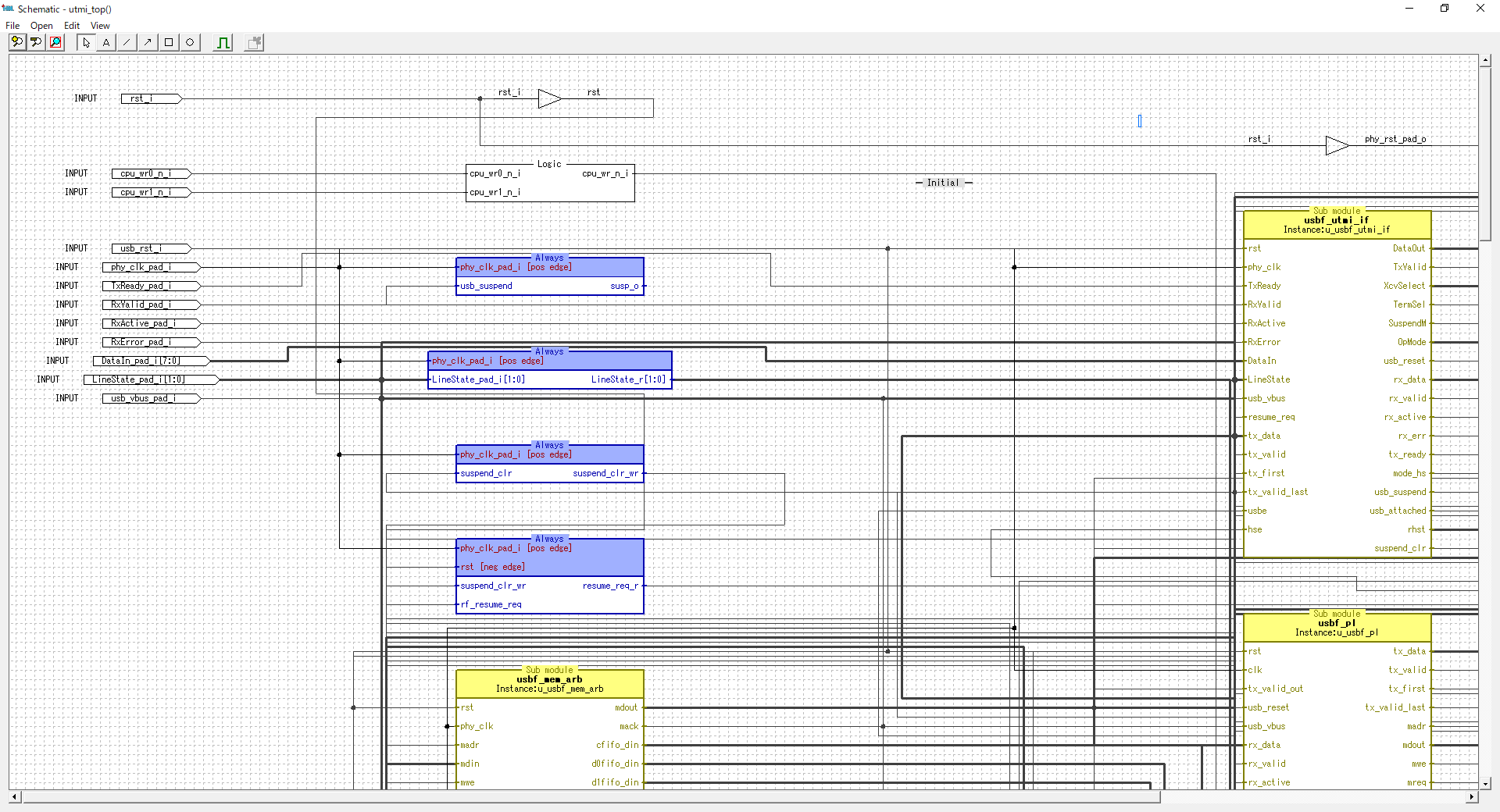

複数のソースファイルからなるプロジェクトをブロック図表示

複数のソースファイルからなるプロジェクトをブロック図表示

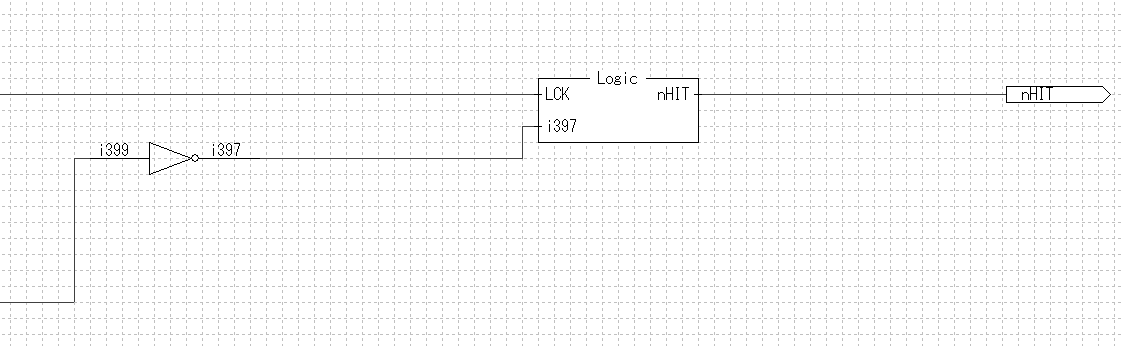

レジスタ1つのみの単純なソースの解析例。

レジスタ1つのみの単純なソースの解析例。 センシティビティリスト(駆動クロックなど)を別枠でみやすく表示。

センシティビティリスト(駆動クロックなど)を別枠でみやすく表示。

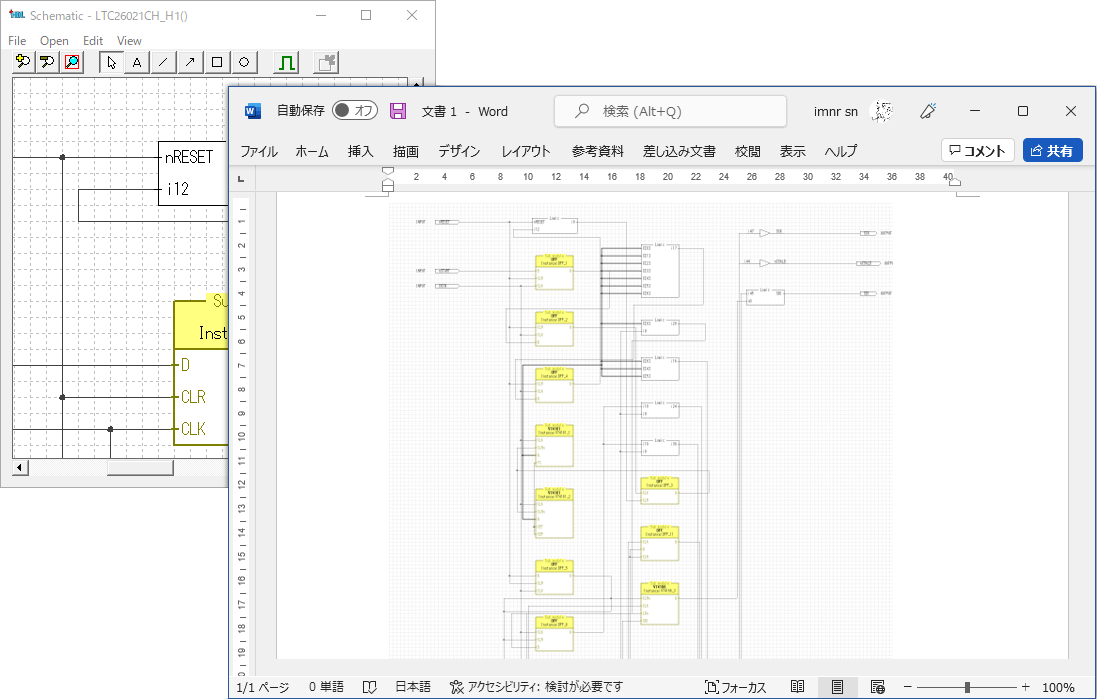

下位モジュールはこのようにイエローで表示されます。

下位モジュールはこのようにイエローで表示されます。 下位モジュールをブロック図として開くこともでき、順次より深い階層のモジュールを追っていくことが可能。

下位モジュールをブロック図として開くこともでき、順次より深い階層のモジュールを追っていくことが可能。

単純な箱で表現されます。

単純な箱で表現されます。 NOT(反転)は、そのまま NOT シンボルで表示。

NOT(反転)は、そのまま NOT シンボルで表示。

BMP 形式でクリップボードへコピーが可能。

BMP 形式でクリップボードへコピーが可能。 より詳細な貼り付けデータが必要となる場合は、EMF 形式ファイルへのエクスポートを利用できます。EMFファイルは、Microsoft®Word などへ挿入が可能です。

より詳細な貼り付けデータが必要となる場合は、EMF 形式ファイルへのエクスポートを利用できます。EMFファイルは、Microsoft®Word などへ挿入が可能です。 ステートマシンを図でわかりやすく表示

ステートマシンを図でわかりやすく表示

ステートマシンを自動的に検知・解析して表示します

ステートマシンを自動的に検知・解析して表示します always節(Verilog) / process節(VHDL)では、記述内容をステートマシン図として表示できます。

always節(Verilog) / process節(VHDL)では、記述内容をステートマシン図として表示できます。 状態変数、各ステートへの遷移条件、および遷移時に値が変化する信号を、すべて自動的に検出し、図を作成します。

状態変数、各ステートへの遷移条件、および遷移時に値が変化する信号を、すべて自動的に検出し、図を作成します。

BMP 形式でクリップボードへコピーが可能です。

BMP 形式でクリップボードへコピーが可能です。

プロジェクトを自動解析、階層構造を表示

プロジェクトを自動解析、階層構造を表示

ヒエラルキー・ウィンドウには、解析中のプロジェクトのソースコードの階層構造が表示されます。

ヒエラルキー・ウィンドウには、解析中のプロジェクトのソースコードの階層構造が表示されます。 解析はフルオート。パラメータの類を指定する必要はありません。

解析はフルオート。パラメータの類を指定する必要はありません。 不足しているソースコードのファイル名も確認できます。

不足しているソースコードのファイル名も確認できます。 信号の飛び先をまとめて表示するネット機能

信号の飛び先をまとめて表示するネット機能 充実のテキスト・レポート

充実のテキスト・レポート

ソースコードで使用しているレジスタ数のレポート機能で、回路規模を簡単に見積もり。下位モジュールのインスタンスの分も合算されますので、見積もりサイズを誤ることもありません。

ソースコードで使用しているレジスタ数のレポート機能で、回路規模を簡単に見積もり。下位モジュールのインスタンスの分も合算されますので、見積もりサイズを誤ることもありません。 他にも、特定の信号の接続や、階層構造なども、テキスト形式でレポート可能です。

他にも、特定の信号の接続や、階層構造なども、テキスト形式でレポート可能です。 Verilog HDL / VHDL 混在プロジェクトに対応

Verilog HDL / VHDL 混在プロジェクトに対応